2. Alat dan Bahan

[Kembali]

1. Module D'Lorenzo

2.Jumper

3.Panel DL 2203C

4..Panel DL 2203D

5.. Panel DL 2203S

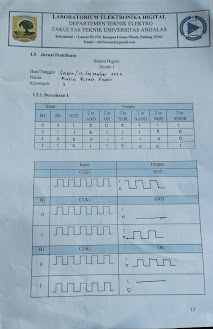

Pada rangkaian pertama ini kita menghubungkan input B0 dan B1 ke gerbang NOT, 2 input gerbang AND, 2 input gerbang OR,2 input gerbang XOR , 2 input gerbang NAND , 2 input gerbang NOR, 2 input gerbang XNOR. Kemudian gerbang gerbang tersebut outputnya dihubungkan ke channel H1,H2.H3,H4,H5,H6.H7. kemudian kita atur input B0 dan B1 nya di keadaan 4 kondisi yaitu saat B0 dan B1 (0,0) (0,1) (1 0) (1 1). kemudian amati hasil outputnya di channel H. sistem kerjanya sama dengan sistem kerja gerbang logika yaitu

1. Gerbang AND : operasi perhitungan dengan perkalian beberapa inputnya menghasilkan 1 output

2. Gerbang OR : operasi perhitungan dengan menjumlahkan beberapa inputnya menghasilkan 1 output

3. Gerbang NAND : operasinya sama dengan gerbang AND namun ditambahkan dengan inverter (NOT) yang menyebabkan berkebalikan hasil outputnya dengan AND

4. Gerbang NOR : operasinya sama dengan gerbang OR namun ditambahkan dengan inverter ( NOT) yang menyebabkan berkebalikan hasil outputnya

dengan OR

5. Gerbang XOR : operasinya jika beberapa input berjumlah ganjil maka ouputnya 1, jika jumlah input nya genap maka outputnya 0

6. Gerbang NOT : operasinya nilai input bertolak belakang dengan nilai outputnya

7. Gerbang X NOR : operasinya sama dengan gerbang XOR namun disambungkan dengan inverter yang menyebabkan berkebalikan hasil outputnya

Untuk input B1 nya kita pindahkan ke clock kemudian B0 nya kita atur kondisinya sesuai dengan jurnal maka akan terlihat output pada Channel H yang dimana output gerbang gerbang logika akan berlawanan dengan output clock

5. Video Rangkaian

[Kembali]

Percobaan 1

1. Analisa pengaruh input untuk output pada tabel pertama

Jawab :

Dapat dilihat dari output pada percobaan pertama semua sesuai dengan tabel kebenaran dimana :

- NOT - Nilai dari outputnya akan beralawanan dengan inputnya

- AND - Nilai outputnya merupakan hasil perkalian, ketika salah satu outputnya bernilai 0 maka outputnya akan 0

- OR - Nilai outputnya merupakan hasil penjumlahan , ketika salah satu outputnya bernilai 1 maka outputnya akan 1

- NAND - Merupakan AND yang memilikki NOT/inverter maka outputnya berkebalikan dengan AND

- XOR - Ketika input bernilai sama maka outputnya akan 0

- NOR - Merupakan OR yang memilikki NOT/inverter maka outputnya berkebalikan dengan OR

- XNOR - Merupakan XOR yang memilikki NOT/inverter maka outpitnya berkebalikan dengan XOR

2. Analisa pengaruh clock untuk setiap output pada gerbang logika

Jawab :

1. Pada gerbang NOT : output yang dikeluarkan berbeda atau bertolak belakang dengan output clock

2. Pada gerbang AND : ketika B0=0 output AND mati/0 digambarkan grafik lurus, ketika B0=1 output AND sama dengan output clock

3. Pada gerbang OR : ketika B0=0 output OR sama dengan output clock, ketika B0=1 output OR selalu hidup digambarkan dengan grafik lurus 1

4. Pada gerbang XOR : ketika B0=0 output XOR sama dengan output clock, ketika B0=1 output XOR berbeda dengan output clock

5. Pada gerbang NAND : ketika B0=0 output NAND selalu hidup ditandai dengan gambar grafik 1 lurus, ketika B0=1 output NAND bertolak belakang dengan output clock

6. Pada gerbang NOR : ketika B0=0 output NOR berbeda dengan output clock, ketika B0=1 output NOR selalu mati digambarkan dengan grafik lurus 0

7. Pada gerbang XNOR : ketika B0=0 output XNOR bertolak belakang dengan output clock, ketika B0=1 output XNOR sama dengan output clock

Pengaruh clock pada setiap output logika adalah menentukan kapan dan bagaimana output gerbang logika akan berubah dan juga menentukan frekuensi seberapa cepat data dapat diproses. Pada percobaan output yang menggunakan input clock, menentukan awal gelombang yang membentuk garis lurus yang juga disebabkan clock.

7. Link Download

[Kembali]

Download Datasheet Gerbang Logika klik disini

Download Datasheet Logicprobe klik disini

Download Datasheet SPDT klik disini

.png)

.png)

Tidak ada komentar:

Posting Komentar